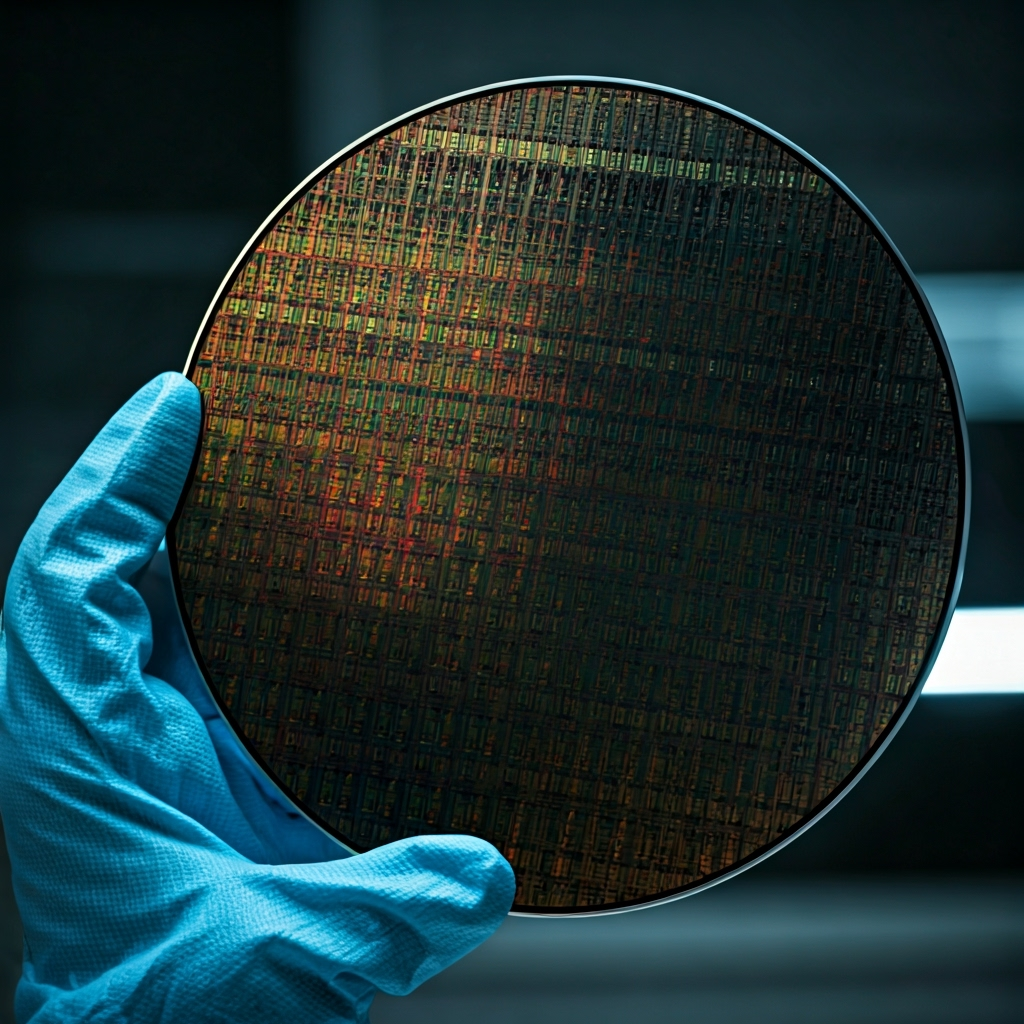

Taiwan Semiconductor Manufacturing Co. (TSMC), der weltweit führende Chiphersteller, hat seinen A16-Chipherstellungsprozess der nächsten Generation vorgestellt – eine bedeutende Weiterentwicklung, die die nächste Welle der künstlichen Intelligenz und des Hochleistungsrechnens (HPC) vorantreiben wird. Die auf dem North America Technology Symposium vorgestellte A16-Technologie wird zwei wichtige Innovationen integrieren: fortschrittliche Nanosheet-Transistoren und ein hochmodernes rückseitiges Stromversorgungsnetzwerk namens Super Power Rail (SPR).

Die Einführung der rückseitigen Stromversorgung stellt einen entscheidenden Architekturwechsel dar. Traditionell konkurrieren Strom- und Datensignale um Platz auf der Vorderseite eines Siliziumwafers. Durch die Verlagerung des Stromversorgungsnetzwerks auf die Rückseite des Wafers schafft der A16-Prozess von TSMC wertvollen Platz auf der Vorderseite und ermöglicht optimierte und effizientere Signalverbindungen. Diese Trennung ist entscheidend für komplexe, stromhungrige Prozessoren wie die KI-Beschleuniger, die moderne Rechenzentren antreiben.

Laut TSMC wird diese Innovation erhebliche Leistungssteigerungen bringen. Im Vergleich zum N2P-Prozess soll die A16-Technologie bei gleicher Spannung eine Geschwindigkeitssteigerung von 8-10% bzw. eine Reduzierung des Stromverbrauchs um 15-20% bei gleicher Geschwindigkeit ermöglichen. Sie ermöglicht zudem eine höhere Transistordichte, die für logikintensive HPC-Anwendungen unerlässlich ist.

Dieser Schritt positioniert TSMC in einem erbitterten Technologiewettlauf mit Konkurrenten wie Intel, das seine konkurrierende PowerVia-Backside-Power-Technologie früher einführen wird. TSMCs Roadmap sieht jedoch die zweite Jahreshälfte 2026 für die A16-Produktion vor und orientiert sich damit an den Entwicklungszyklen seiner wichtigsten Kunden, darunter Apple, Nvidia und AMD, die für ihre zukünftigen Produkte auf diese fortschrittlichen Knotenpunkte setzen. Der A16-Prozess unterstreicht das unermüdliche Streben der Branche nach Leistungs- und Effizienzsteigerungen, die für die anhaltende KI-Revolution erforderlich sind.